動作中の半導体p-n接合ダイオードの電位分布の観察に成功

~高性能半導体デバイスの研究開発を促進~

2018年6月28日

I【概要】

① 現状と課題

昨今、高性能化が進む半導体デバイスの研究開発において、動作中の半導体素子の電位分布を正確に評価することがますます重要となっています。これまで、半導体素子の電位分布の観察には、電子線ホログラフィー注1が用いられてきました。しかし、電圧印加に伴う微小な電位分布変化を正確に観察するには、従来の電子線ホログラフィー(フーリエ変換法)では空間分解能と感度が不十分でした。また、電子顕微鏡内の試料への電圧印加も技術的に困難であることから、動作中の半導体素子の電位分布を観察したという報告例はほとんど存在しません。

② 本研究の成果

JFCCは高空間分解能(1 nm)且つ高感度(0.01 V)の計測が可能な電子線ホログラフィー(位相シフト法)と電子顕微鏡内の試料への電圧印加技術を独自に開発し、古河電気工業(株)と東京大学大学院工学系研究科と共同で、動作中の砒化ガリウム(GaAs)p-n接合ダイオードの電位分布を高精度に計測することに成功しました。

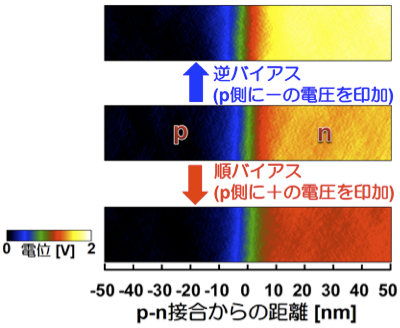

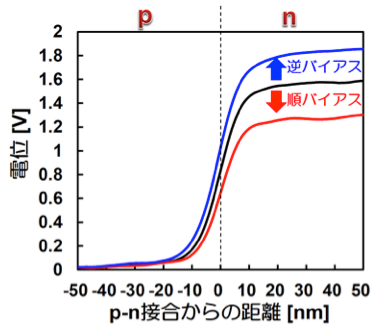

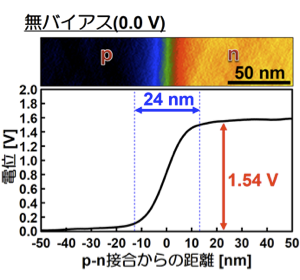

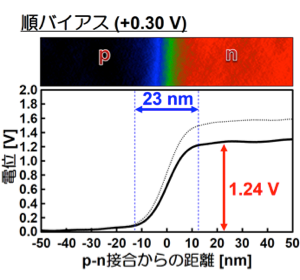

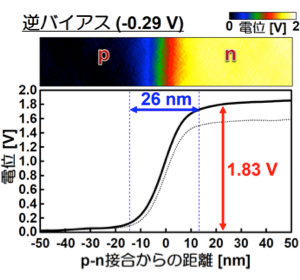

図1:電圧印加に伴うGaAs p-n接合の電位分布変化

③ 今後の展開

今後、本計測技術を用いて、トランジスタや発光素子など、より複雑なデバイスについて研究を進めていく予定です。実際に動作している半導体素子の電位挙動を深く理解することで、より高効率なデバイス設計が可能となり、高性能デバイスの開発に役立つことが期待されます。

本研究成果は、下記に開催の2018年度JFCC研究成果発表会で発表しました。

7月6日(金)(東京会場:東京大学武田先端知ビル武田ホール)

7月13日(金)(名古屋会場:愛知県産業労働センター(ウインクあいち2F、5F))

7月20日(金)(大阪会場:梅田スカイビル(タワーウエスト36F))

本成果は2017年12月12日に「Journal of Applied Physics」電子版で出版されました。

本研究の一部は、文部科学省先端研究基盤共用促進事業(共用プラットフォーム形成支援プログラム)の支援を受けて行いました。

用語説明

注1) 電子線ホログラフィー

透過型電子顕微鏡を用いた計測手法の一つであり、電位や磁位を定量的に観察できる特長を有する。試料を透過した電子波(物体波)と真空中を通過してきた電子波(参照波)を干渉させ、試料の電位情報を記録した電子波干渉パターン(ホログラム)をCCDカメラで撮影する。その後、ホログラムを画像解析することにより、試料の電位分布を可視化することができる。

II【本研究の詳細】

① 研究の背景

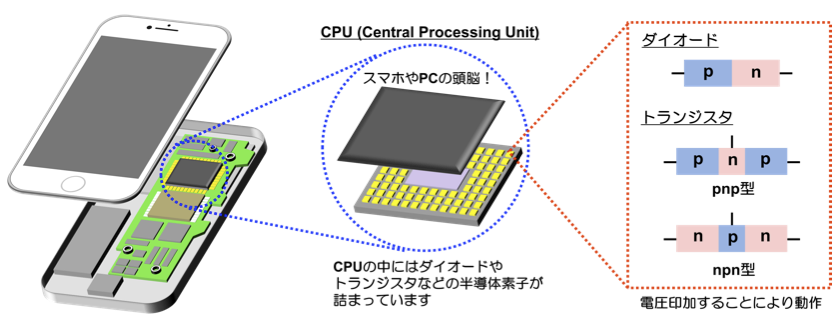

情報化社会の根幹を成す半導体素子は、様々な種類のp型半導体注2やn型半導体注3を組み合わせることで、ダイオードやトランジスタとして動作します。

これら半導体素子の動作原理は、電圧印加時の電位分布の変化と密接に関係しています。微細化による性能向上が限界を迎えつつある昨今の半導体デバイスの研究開発においては、この電位分布変化を正確に評価することが益々重要となっています。これまで、半導体素子の電位分布の観察には、電子線ホログラフィーが用いられてきました。しかし、電圧印加による半導体素子の電位分布変化は、ナノメートルスケールの非常に狭い領域で起こり、変化量も1 V以下と微小なため、この変化を正確に評価するには従来の電子線ホログラフィー(フーリエ変換法)では空間分解能と感度が不十分でした。また、電子顕微鏡内の試料に電圧を印加すること自体も技術的に困難であるため、動作中の半導体素子を観察したという報告例はほとんど存在せず、電位分布の詳細は明らかとなっていないのが現状です。

② 実験方法

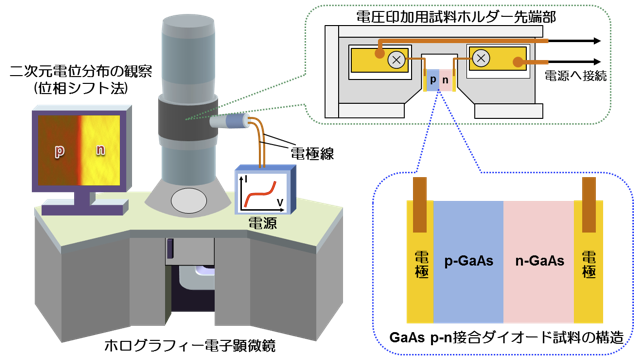

JFCCは、古河電気工業(株)と東京大学大学院工学系研究科柴田直哉教授らと共同で、動作中の砒化ガリウム(GaAs)のp-n接合ダイオード注4の電位分布を観察しました。図3は、電圧印加時の試料の電位分布観察方法を模式的に示しています。電位分布観察は、JFCCが独自に開発した世界最高レベルの空間分解能と感度を誇る電子線ホログラフィー(位相シフト法)を用いて実施しました。電子顕微鏡内の試料への電圧印加は、電極を取り付けたバルク試料の一部を薄膜化した後、JFCCが開発した電圧印加用試料ホルダーにセットし、外部電源と電気的に接続することで可能としました。

③ 研究成果

電子線ホログラフィーの結果、電圧印可時のGaAs p-n接合の電位分布を正確に計測することに成功しました。図4は、左から、無バイアス(電圧印加なし)、順バイアス(p側に+0.30 V)、逆バイアス(p側に-0.29 V)時のGaAs p-n接合の二次元電位分布像と電位プロファイルを示しています。二次元電位分布像では、電圧印加による電位分布変化が明瞭に可視化されています。電位プロファイルでは、p-n間の電位差と空乏層幅が、順バイアスで減少し、逆バイアスで増大している様子が定量的に示されています。電圧印加によるp-n間の電位差と空乏層幅の変化量は、それぞれ0.3 Vと1 nm程度と微小ですが、位相シフト法を用いることにより、これらを高精度に観察することができました。

図4:GaAs p-n接合の二次元電位分布像と電位プロファイル

④ 今後の展開

今後、トランジスタや発光素子など、より複雑な半導体素子の観察や不良解析に本計測技術を応用していきます。動作中の半導体素子の電位分布の詳細を明らかにすることで、スーパーコンピュータや通信用の高周波デバイスに用いられる高性能半導体素子の研究開発が促進されるものと期待されます。

用語説明

注2) p型半導体

正孔が電荷を運ぶ担い手(キャリア)として働く半導体である。正孔は電子が抜けた孔であり、正の電荷を持つ。砒化ガリウム(GaAs)化合物半導体では、炭素(C)などの元素を微量に添加することによって作られる。

注3) n型半導体

電子がキャリアとして働く半導体である。電子は負の電荷を持つ。GaAs化合物半導体では、シリコン(Si)などの元素を微量に添加することによって作られる。

注4) p-n接合ダイオード

p型半導体とn型半導体を接合させた半導体素子であり。接合界面の近傍では、正孔と電子が打ち消しあい、キャリアが存在しない領域(空乏層)が生じる。また、空乏層では、p側にマイナス、n側にプラスの電荷が存在し、p-n間に電位差(内蔵電位)が生じる。